|

Le bus I²C |

Introduction

Le bus I²C (Inter Integrated Circuit) fait partie des bus série : 3 fils pour faire tout passer. Il a été développé au début des années 1980, par Philips pour minimiser les liaisons entre les circuits intégrés numériques de ses produits (Téléviseurs, éléments HiFi, magnétoscopes, ...).

Aujourd'hui, Philips a dans son catalogue plus de 150 circuits intégrés CMOS et bipolaires qui sont compatibles I²C. D'autres fabricants ont aussi développé des circuits intégrés qui peuvent être connectés au bus I²C. Le protocole utilisé est simple et rapide.

Caractéristiques

Le bus I²C permet de faire communiquer entre eux des composants électroniques très divers grâce à seulement trois fils : un signal de données (SDA), un signal d'horloge (SCL), et un signal de référence électrique (masse).

Il s'agit d'une liaison en mode série, ce qui signifie que la vitesse de transfert sera plus faible qu'avec un bus de type parallèle. Le bus I²C permet cependant des échanges à la vitesse de 100 kbits par seconde. Certes, la vitesse de transfert du bus I²C n'est pas fulgurante, mais dans bien des cas, la vitesse n'est pas l'élément prédominant.

L'utilisation d'un bus I²C permet de réduire la complexité des circuits imprimés à réaliser. Par exemple, pour connecter une EEPROM ou une RAM à un micro contrôleur classique, il faut relier entre eux les bits de données et les bits d'adresses des différents composants, et, en plus, il faut bien souvent ajouter une logique de sélection. Avec des composants prévus pour se connecter au bus I²C, il suffit de les relier par deux pistes seulement. Si, par la suite, on souhaite ajouter des composants sur le circuit, le nombre de pistes à ajouter sera vraiment plus réduit (essayez d'ajouter une EEPROM sur un circuit existant pour voir).

De nombreux fabricants ayant adopté le système, la variété des systèmes disposant d'un port I²C est énorme :

o micro contrôleurs

o expandeurs de bus (entrée/sortie 8 bits)

o convertisseurs A/N et N/A

o mémoires (RAM, EPROM, EEPROM, etc.)

o récepteurs infra-rouge (télécommande RC5)

o capteurs divers

o circuits audio (égaliseur, contrôle de volume, etc.)

o drivers d'affichage LCD ou à LEDs

o décodeurs télétexte

o chargeurs de batterie

o PLL pour tuner HF

o etc.

Le support physique utilisé

Comme indiqué précédemment, pour se connecter à un bus I²C il faut une masse, et deux fils de communication. Le premier fil, SDA (Signal DAta), est utilisé pour transmettre les données. L'autre fil, SCL (Signal CLock) est utilisé pour transmettre un signal d'horloge synchrone (signal qui indique le rythme d'évolution de la ligne SDA). Les tensions associées aux niveaux logiques vont dépendre de la technologie des circuits en présence (CMOS, TTL). Il faudra que tous les circuits connectés au bus I²C utilisent les mêmes potentiels pour définir les niveaux haut et bas. En définitive, cela implique que tous les composants connectés à un même bus soient alimentés de façon identique. Cela ne signifie pas que les composants doivent utiliser la même source pour s'alimenter ; il suffit que la tension d'alimentation soit à la même valeur pour tous les composants, le fil de masse permettant d'unifier les références.

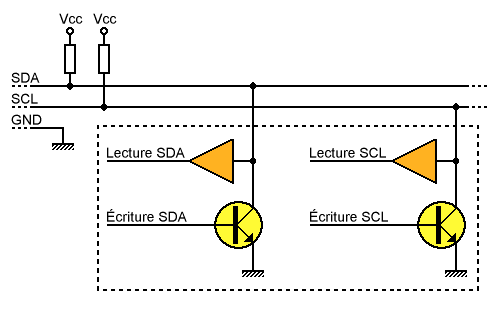

Il reste maintenant un problème crucial. Comment permettre à plusieurs circuits logiques de connecter leurs sorties ensemble, sachant que certains circuits voudront imposer un niveau haut tandis que d'autres voudront imposer un niveau bas ? La réponse est connue depuis longtemps. Il faut utiliser des sorties à collecteur ouvert (ou à drain ouvert pour des circuits CMOS). Le niveau résultant sur la ligne est alors une fonction « ET » de toutes les sorties connectées.

Les résistances de rappel au potentiel VCC permettent aux signaux SDA et SCL d'être à 1 si toutes les sorties à, collecteurs ouverts sont aussi au niveau 1 (résultat de la fonction « ET »). Si une ou plusieurs sorties tentent d'imposer un niveau bas sur une ligne, le ou les transistors associés vont conduire, ce qui entraîne un niveau bas sur la ligne correspondante (ce qui est conforme au résultat de la fonction « ET »).

En ce qui concerne la lecture des signaux SDA et SCL, cela ne pose pas de problème. Les signaux peuvent être lus en permanence sans risque d'interférer sur le niveau de la ligne.

Au repos, tous les circuits connectes doivent imposer un niveau haut sur leurs sorties respectives. Si les lignes SDA et SCL sont au niveau haut dans ces conditions, cela signifie qu'aucun circuit ne tente de prendre le contrôle du bus. Si une des lignes SDA ou SCL passe à un niveau bas dans les mêmes conditions, c'est qu'un des circuits désire prendre le contrôle du bus. Mais il peut aussi y avoir deux circuits qui tentent de prendre le contrôle du bus en même temps (ou à quelques nanosecondes d'écart près). Il faut donc mettre en place un protocole pour gérer les conflits possibles.

Le protocole I²C

Le protocole du bus I²C définit la succession des états possibles sur les lignes SDA et SCL, et comment doivent réagir les circuits en cas de conflit.

La prise de contrôle du bus

Pour transmettre des données sur le bus I²C, il faut surveiller deux conditions particulières : la condition de départ et la condition d'arrêt.

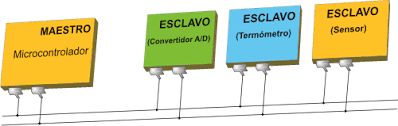

Avant de tenter de prendre le contrôle du bus, un circuit doit vérifier que les lignes SDA et SCL sont au repos, c'est-à-dire à l'état haut. Si c'est le cas, le circuit indique qu'il prend le contrôle du bus en mettant la ligne SDA à 0. A partir de ce moment là, les autres circuits savent que le bus est occupé et ils ne devraient pas tenter d'en prendre contrôle. Le circuit qui vient de prendre le contrôle du bus en devient le maître (en anglais « master »). C'est lui qui génère le signal d'horloge, quel que soit le sens du transfert.

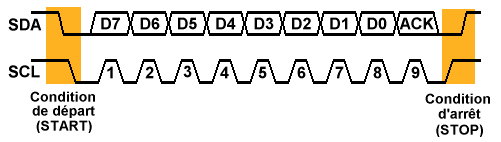

La transmission d'un octet

Avant de placer les bits qui forment l'octet à transmettre sur le bus, le maître doit placer la ligne d'horloge SCL à 0. Tant que la ligne SCL est au niveau haut, la ligne SDA ne doit pas changer d'état, sinon cette condition sera interprétée comme la condition d'arrêt. La condition arrêt peut survenir même au milieu de la transmission d'un octet, pour abandonner la transmission et libérer le bus pour les autres circuits. Pour transmettre correctement les bits sur la ligne SDA, le maître doit donc tout d'abord placer la ligne SCL à 0. Ensuite, le maître peut placer la ligne SDA au niveau correspondant au bit à transmettre et replacer la ligne SCL au niveau 1 pour indiquer que le bit est présent sur la ligne SDA. La même opération va se répéter autant de fois que nécessaire pour transmettre les 8 bits de données. Notez que c'est le bit de poids fort qui est transmis en premier.

Une fois les 8 bits transmis, le circuit qui vient de recevoir les données doit imposer un bit d'acquittement ACK sur la ligne SDA. Pour cela, pendant que la ligne SCL est au niveau bas, le maître place sa propre sortie au niveau haut, tandis que le récepteur (aussi appelé l'esclave) place sa sortie au niveau bas. Puisque les sorties sont à collecteur ouvert, la ligne SDA restera au niveau bas à cause de l'esclave. Le maître relit ensuite la ligne SDA une fois qu'il a passé la ligne SCL au niveau haut. Si la valeur lue pour le bit ACK est 0, c'est que l'esclave s'est bien acquitté de l'octet reçu, sinon c'est qu'il y a une erreur et le maître doit générer la condition arrêt.

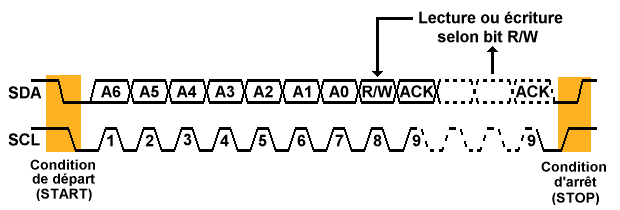

La transmission d'une adresse

Le nombre de composants qu'il est possible de connecter sur un bus I²C étant largement supérieur à deux, le maître doit pouvoir choisir quel esclave est censé recevoir les données. Dans ce but, le premier octet que transmet le maître n'est pas une donnée mais une adresse. Le format de l'octet d'adresse est un peu particulier puisque le bit D0 est réservé pour indiquer si le maître demande une lecture â l'esclave ou bien au contraire si le maître impose une écriture à l'esclave.

Chaque circuit connecté au bus I²C possède une adresse, qui doit être unique. L'adresse associée à un composant est définie en partie par l'état de broches de sélections et d'autre part par sa fonction. Par exemple, le circuit PCF8574, qui est un port d'entrées/sorties bidirectionnel 8 bits, décompose son adresse de la façon suivante : [0] [1] [0] [0] [A2] [A1] [A0] [R/W]. Les bits A2, A1 et A0 reflètent l'état des broches 1, 2 et 3 du circuit. Cela permet de placer 8 circuits PCF8574 sur le bus I²C. Lors de la conception d'un système, il faut donc veiller à l'unicité des adresses attribuées aux différents composants.

Une fois l'adresse envoyée sur le bus, l'esclave concerné doit répondre en plaçant le bit ACK à 0. Si le but ACK vaut 1, le maître comprend qu'il y a une erreur de sélection et il génère la condition arrêt. En revanche, si le bit ACK vaut 0, le maître peut continuer les opérations.

Note : Les adresses 0000 0xxx et 1111 11xx sont réservées à des modes de fonctionnement particuliers.

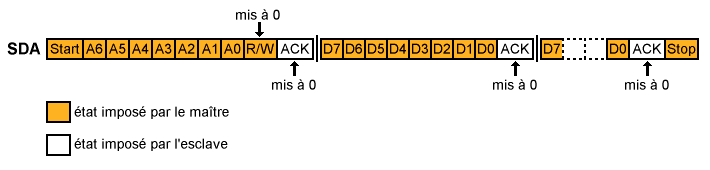

Écriture d'une donnée

Si le bit R/W précédemment envoyé était à 0, cela signifie que le maître doit transmettre un ou plusieurs octets de données. Après chaque bit ACK valide, le maître peut continuer d'envoyer des octets à l'esclave ou bien il peut décider de terminer le dialogue par une condition d'arrêt.

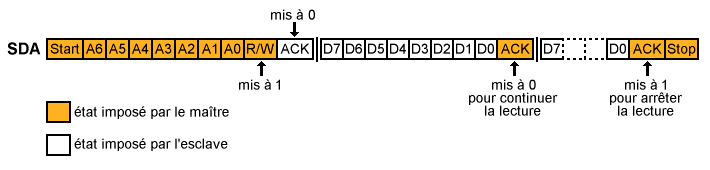

Lecture d'une donnée

Si le bit R/W transmis en même temps que l'adresse est à 1, cela signifie que le maître veut lire des données issues de l'esclave. C'est toujours le maître qui va générer le signal d'horloge SCL. En revanche, après le bit ACK de l'adresse, c'est l'esclave qui va garder le contrôle de la ligne SDA. Pour cela, le maître va placer sa propre sortie SDA au niveau haut pour permettre à l'esclave de prendre le contrôle de la ligne SDA. L'esclave doit alors scruter la ligne SCL et attendre le niveau bas pour changer l'état de la ligne SDA, faute de quoi le maître détectera une condition arrêt et abandonnera le transfert (l'électronique intégrée dans l'esclave se doit de détecter aussi qu'il y a eu une condition arrêt, bien entendu).

Après que l'esclave a transmis les 8 bits de données, c'est le maître, cette fois-ci, qui va générer un bit d'acquittement. Si le maître désire lire des octets supplémentaires, il placera le bit d'acquittement à 0. En revanche, si le maître décide que la lecture est terminée, il placera le bit ACK au niveau 1. L'esclave comprendra alors que le transfert est terminé. Cette fois-ci, bien que le bit ACK soit au niveau 1, cela ne correspond pas à une condition d'erreur mais à une fin de transfert.

Restart

Le protocole du bus I²C ne s'arrête pas là. Il est possible d'enchaîner écriture et lecture de l'esclave sans avoir à passer par une condition arrêt. Par exemple, dans le cas de la lecture d'une RAM, le maître commence par envoyer l'adresse du composant avec le bit R/W positionné sur l'écriture. La RAM adressé, en esclave renvoie ACK = 0. Ensuite, le maître transmet l'adresse interne de la case mémoire demandée. Une fois encore, l'esclave répond par ACK = 0. Le maître envoie alors à nouveau une condition de départ (sans passer par une condition d'arrêt), puis de nouveau l'adresse du composant sélectionné mais en plaçant le bit R/W sur la position lecture. L'esclave va répondre par ACK = 0 et enchaîner par la transmission du contenu de la case mémoire demandée. C'est toujours le maître qui impose l'horloge SCL mais c'est l'esclave, en l'occurrence la RAM, qui contrôle la ligne SDA. Une fois les 8 bits de données transmis par la RAM, si le maître veut lire le contenu de la case mémoire suivante, il placera le bit ACK au niveau 0. Dans ce cas, la RAM recommence la lecture avec la case mémoire suivante. En revanche, si le maître souhaite en terminer avec la lecture, il placera le bit ACK au niveau 1 et il générera ensuite la condition arrêt.

Le contenu des octets de données lus ou écrits aura une signification qui dépend du composant sélectionné. Mais le protocole reste le même.

Pour en savoir plus sur le bus I²C :

Vous pouvez consulter le document The I²C-bus and how to use it (including specifications) de Philips Semiconductors.

Créé avec HelpNDoc Personal Edition: Produire des livres EPub gratuitement