|

Étude du DS1307 |

I - Étude de la documentation constructeur du DS1307

Datasheet du DS1307

Datasheet du DS1307

|

BENEFITS AND FEATURES

|

AVANTAGES ET CARACTÉRISTIQUES

|

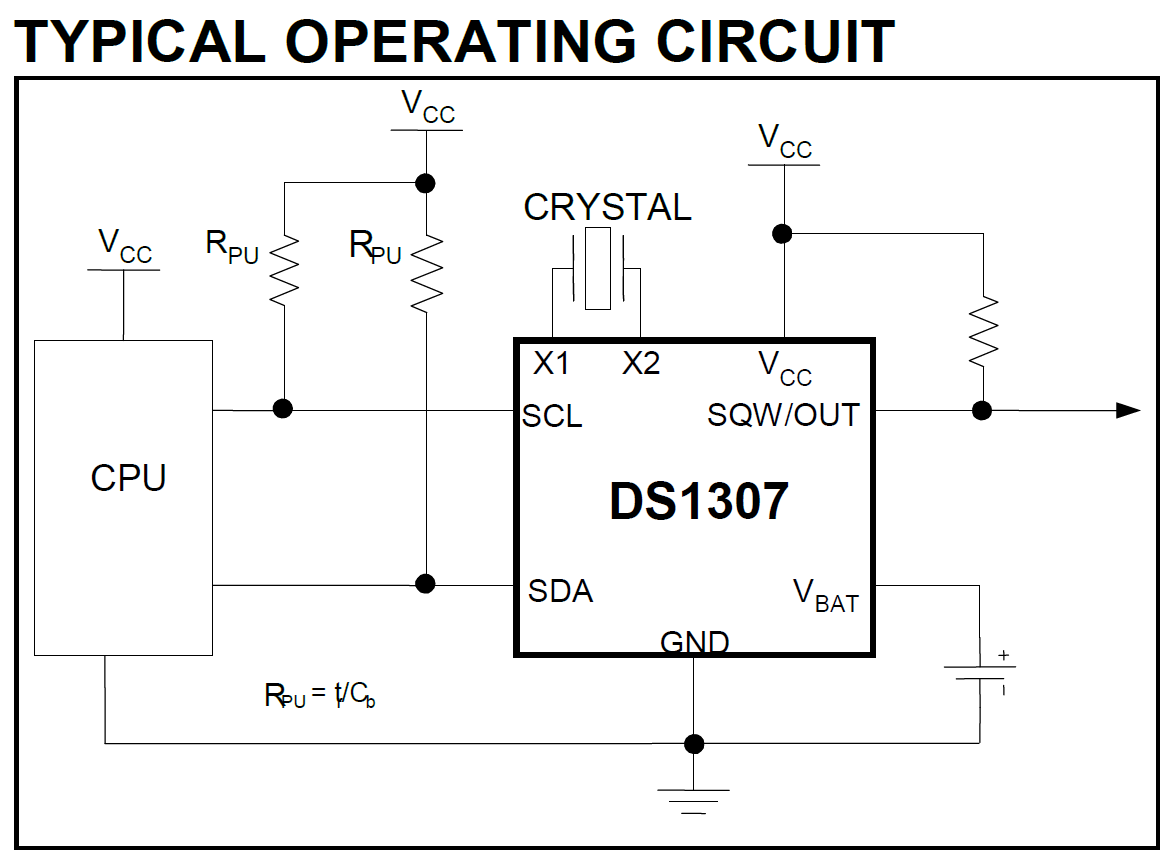

GENERAL DESCRIPTION

The DS1307 serial real-time clock (RTC) is a low-power, full binary-coded decimal (BCD) clock/calendar plus 56 bytes of NV SRAM. Address and data are transferred serially through an I2C, bidirectional bus. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The end of the month date is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. The DS1307 has a built-in power-sense circuit that detects power failures and automatically switches to the backup supply. Timekeeping operation continues while the part operates from the backup supply.

DESCRIPTION GÉNÉRALE

L'horloge en temps réel (HTR) série DS1307 est une horloge/calendrier décimal codé binaire (DCB) à faible consommation, qui possède en plus 56 octets de mémoire de type NV SRAM (non-volatile random-access memory). L'adresse et les données sont transférées en série via un bus bidirectionnel I2C. L'horloge/calendrier fournit des informations sur les secondes, les minutes, les heures, le jour de la semaine, la date, le mois et l'année. La date de fin de mois est automatiquement ajustée pour les mois de moins de 31 jours, y compris les corrections pour les années bissextiles. L'horloge fonctionne au format 24 heures ou 12 heures avec indicateur AM/PM. Le DS1307 dispose d'un circuit de détection de puissance intégré qui détecte les coupures de courant et passe automatiquement à l'alimentation de secours. Le fonctionnement de l'horloge continue alors que le composant fonctionne à partir de l'alimentation de secours.

PIN DESCRIPTION

|

PIN |

NAME |

FUNCTION |

|

1 |

X1 |

Connections for Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance (CL) of 12.5pF. X1 is the input to the oscillator and can optionally be connected to an external 32.768kHz oscillator. The output of the internal oscillator, X2, is floated if an external oscillator is connected to X1. Note: For more information on crystal selection and crystal layout considerations, refer to Application Note 58: Crystal Considerations with Dallas Real-Time Clocks. |

|

2 |

X2 |

|

|

3 |

VBAT |

Backup Supply Input for Any Standard 3V Lithium Cell or Other Energy Source. Battery voltage must be held between the minimum and maximum limits for proper operation. Diodes in series between the battery and the VBAT pin may prevent proper operation. If a backup supply is not required, VBAT must be grounded. The nominal power-fail trip point (VPF) voltage at which access to the RTC and user RAM is denied is set by the internal circuitry as 1.25 x VBAT nominal. A lithium battery with 48mAh or greater will back up the DS1307 for more than 10 years in the absence of power at +25°C. UL recognized to ensure against reverse charging current when used with a lithium battery. Go to: www.maxim-ic.com/qa/info/ul/. |

|

4 |

GND |

Ground |

|

5 |

SDA |

Serial Data Input/Output. SDA is the data input/output for the I2C serial interface. The SDA pin is open drain and requires an external pullup resistor. The pullup voltage can be up to 5.5V regardless of the voltage on VCC. |

|

6 |

SCL |

Serial Clock Input. SCL is the clock input for the I2C interface and is used to synchronize data movement on the serial interface. The pullup voltage can be up to 5.5V regardless of the voltage on VCC. |

|

7 |

SQW/OUT |

Square Wave/Output Driver. When enabled, the SQWE bit set to 1, the SQW/OUT pin outputs one of four square-wave frequencies (1Hz, 4kHz, 8kHz, 32kHz). The SQW/OUT pin is open drain and requires an external pullup resistor. SQW/OUT operates with either VCC or VBAT applied. The pullup voltage can be up to 5.5V regardless of the voltage on VCC. If not used, this pin can be left floating. |

|

8 |

VCC |

Primary Power Supply. When voltage is applied within normal limits, the device is fully accessible and data can be written and read. When a backup supply is connected to the device and VCC is below VTP, read and writes are inhibited. However, the timekeeping function continues unaffected by the lower input voltage. |

DESCRIPTION DES BROCHES

|

BROCHE |

NOM |

FONCTION |

|

1 |

X1 |

Connexions pour un cristal de quartz standard 32,768 kHz. Le circuit de l'oscillateur interne est conçu pour fonctionner avec un cristal ayant une capacité de charge spécifiée (CL) de 12,5 pF. X1 est l'entrée de l'oscillateur et peut éventuellement être connecté à un oscillateur externe de 32,768 kHz. La sortie de l'oscillateur interne, X2, est flottante si un oscillateur externe est connecté à X1. Remarque : Pour plus d'informations sur la sélection du quartz et les conditions relatives à sa disposition, reportez-vous à la note d'application 58 : Crystal Considerations with Dallas Real-Time Clocks.. |

|

2 |

X2 |

|

|

3 |

VBAT |

Entrée d'alimentation de secours pour toute cellule au lithium 3 V standard ou autre source d'énergie. La tension de la batterie doit être maintenue entre les limites minimale et maximale pour un bon fonctionnement. Les diodes en série entre la batterie et la broche VBAT peuvent empêcher le bon fonctionnement. Si une alimentation de secours n'est pas nécessaire, VBAT doit être mis à GND. La tension nominale du point de déclenchement de coupure de courant (VPF) à laquelle l'accès au RTC et à la RAM de l'utilisateur est refusé, est définie à 1,25 x VBAT nominal. Une batterie au lithium de 48 mAh ou plus sauvegardera le DS1307 pendant plus de 10 ans en l'absence d'alimentation à +25 °C. Reconnu par UL (abréviation de Underwriters Laboratories) pour assurer le courant de charge lorsqu'il est utilisé avec une batterie au lithium. |

|

4 |

GND |

Ground |

|

5 |

SDA |

Entrée/sortie de données série. SDA est l'entrée/sortie de données pour l'interface série I2C. La broche SDA est à drain ouvert et nécessite une résistance de rappel à l'état haut (pullup) externe. La tension de pullup peut atteindre 5,5 V quelle que soit la tension sur VCC. |

|

6 |

SCL |

Entrée d'horloge série. SCL est l'entrée d'horloge pour l'interface I2C et est utilisée pour synchroniser le mouvement des données sur l'interface série. La tension de pullup peut atteindre 5,5 V quelle que soit la tension sur VCC. |

|

7 |

SQW/OUT |

Pilote d'onde carrée/sortie. Lorsqu'il est activé, le bit SQWE réglé sur 1, la broche SQW/OUT produit l'une des quatre fréquences d'onde carrée (1Hz, 4kHz, 8kHz, 32kHz). La broche SQW/OUT est à drain ouvert et nécessite une résistance pullup externe. SQW/OUT fonctionne avec VCC ou VBAT appliqué. La tension de pullup peut atteindre 5,5 V quelle que soit la tension sur VCC. Si elle n'est pas utilisée, cette broche peut être laissée flottante. |

|

8 |

VCC |

Alimentation principale. Lorsque la tension appliquée est dans les limites normales, le composant est entièrement accessible et les données peuvent être écrites et lues. Lorsqu'une alimentation de secours est connectée au composant et que VCC est inférieur à VTP, la lecture et l'écriture sont inhibées. Cependant, la fonction de chronométrage n'est pas affectée par la tension d'entrée inférieure. |

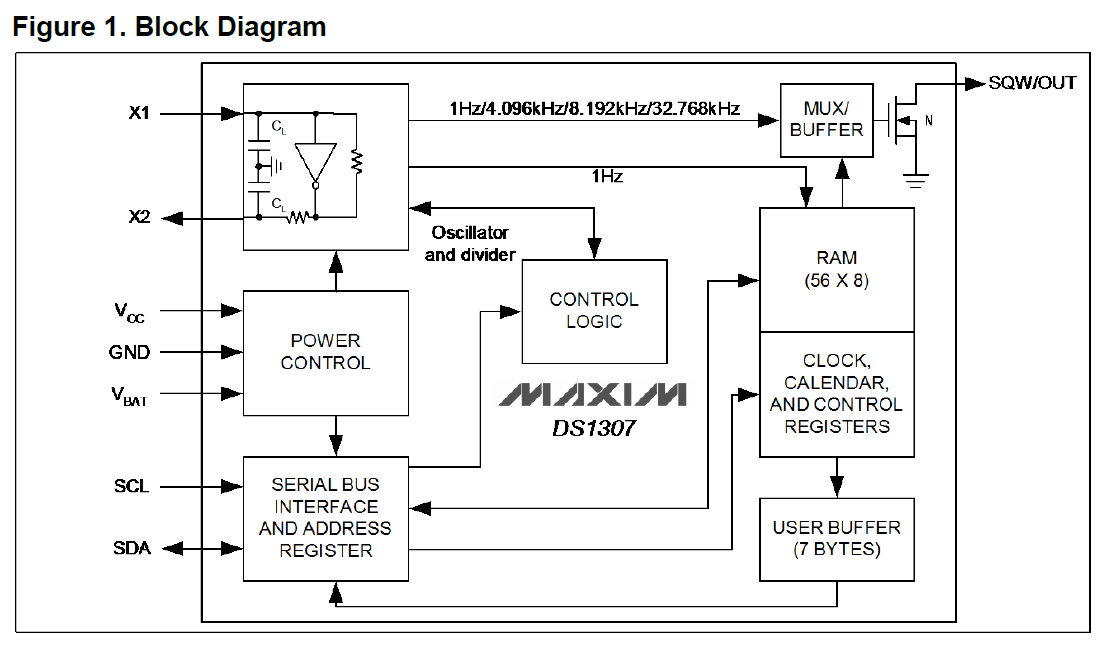

DETAILED DESCRIPTION

The DS1307 is a low-power clock/calendar with 56 bytes of battery-backed SRAM. The clock/calendar provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The DS1307 operates as a slave device on the I2C bus. Access is obtained by implementing a START condition and providing a device identification code followed by a register address. Subsequent registers can be accessed sequentially until a STOP condition is executed. When VCC falls below 1.25 x VBAT, the device terminates an access in progress and resets the device address counter. Inputs to the device will not be recognized at this time to prevent erroneous data from being written to the device from an out-of-tolerance system. When VCC falls below VBAT, the device switches into a low-current battery-backup mode. Upon power-up, the device switches from battery to VCC when VCC is greater than VBAT +0.2V and recognizes inputs when VCC is greater than 1.25 x VBAT. The block diagram in Figure 1 shows the main elements of the serial RTC.

DESCRIPTION DÉTAILLÉE

Le DS1307 est une horloge/calendrier basse consommation avec 56 octets de SRAM sauvegardée par batterie. L'horloge/calendrier fournit des informations sur les secondes, les minutes, les heures, le jour, la date, le mois et l'année. La date de fin de mois est automatiquement ajustée pour les mois de moins de 31 jours, y compris les corrections pour les années bissextiles. Le DS1307 fonctionne comme esclave sur le bus I2C. L'accès est obtenu en implémentant une condition START et en fournissant un code d'identification de dispositif suivi d'une adresse de registre. Les registres suivants peuvent être accédés séquentiellement jusqu'à ce qu'une condition STOP soit exécutée. Lorsque VCC tombe en dessous de 1,25 x VBAT, le composant met fin à l'accès en cours et réinitialise le compteur d'adresses interne. Les entrées du composant ne sont plus reconnues à ce moment pour empêcher l'écriture de données erronées à partir d'un système hors tolérance. Lorsque VCC tombe en dessous de VBAT, le composant passe en mode de batterie de secours à faible courant. Lors de la mise sous tension, l'alimentation du composant passe de la batterie à VCC, lorsque VCC est supérieur à VBAT +0,2V et reconnaît les entrées lorsque VCC est supérieur à 1,25 x VBAT. Le schéma fonctionnel de la figure 1 montre les principaux éléments du RTC série.

CLOCK AND CALENDAR

The time and calendar information is obtained by reading the appropriate register bytes. Table 2 shows the RTC registers. The time and calendar are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in the BCD format. The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on.) Illogical time and date entries result in undefined operation. Bit 7 of Register 0 is the clock halt (CH) bit. When this bit is set to 1, the oscillator is disabled. When cleared to 0, the oscillator is enabled. On first application of power to the device the time and date registers are typically reset to 01/01/00 01 00:00:00 (MM/DD/YY DOW HH:MM:SS). The CH bit in the seconds register will be set to a 1. The clock can be halted whenever the timekeeping functions are not required, which minimizes current (IBATDR).

The DS1307 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12-hour or 24-hour mode-select bit. When high, the 12-hour mode is selected. In the 12-hour mode, bit 5 is the AM/PM bit with logic high being PM. In the 24-hour mode, bit 5 is the second 10-hour bit (20 to 23 hours). The hours value must be re-entered whenever the 12/24-hour mode bit is changed.

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on any I2C START. The time information is read from these secondary registers while the clock continues to run. This eliminates the need to re-read the registers in case the internal registers update during a read. The divider chain is reset whenever the seconds register is written. Write transfers occur on the I2C acknowledge from the DS1307. Once the divider chain is reset, to avoid rollover issues, the remaining time and date registers must be written within one second.

HORLOGE ET CALENDRIER

Les informations d'heure et de calendrier sont obtenues en lisant les octets de registre appropriés. Le tableau 2 montre les registres RTC. L'heure et le calendrier sont définis ou initialisés en écrivant les octets de registre appropriés. Le contenu des registres de l'heure et du calendrier est au format DCB. Le registre des jours de la semaine s'incrémente à minuit. Les valeurs qui correspondent au jour de la semaine sont définies par l'utilisateur mais doivent être séquentielles (par exemple, si 1 est égal à dimanche, alors 2 est égal à lundi, et ainsi de suite.) Les entrées d'heure et de date illogiques entraînent une opération indéfinie. Le bit 7 du registre 0 est le bit d'arrêt d'horloge (CH). Lorsque ce bit est mis à 1, l'oscillateur est désactivé. Lorsqu'il est remis à 0, l'oscillateur est activé. Lors de la première mise sous tension du composant, les registres d'heure et de date sont généralement réinitialisés à 01/01/00 01 00:00:00 (MM/DD/YY DOW HH:MM:SS). Le bit CH dans le registre des secondes sera mis à 1. L'horloge peut être arrêtée chaque fois que les fonctions de chronométrage ne sont pas nécessaires, ce qui minimise le courant (IBATDR).

Le DS1307 peut fonctionner en mode 12 heures ou 24 heures. Le bit 6 du registre des heures est défini comme le bit de sélection de mode 12 heures ou 24 heures. Lorsqu'il est au niveau haut, le mode 12 heures est sélectionné. En mode 12 heures, le bit 5 est le bit AM/PM, le niveau logique haut indique PM. En mode 24 heures, le bit 5 est le deuxième bit de 10 heures (20 à 23 heures). La valeur des heures doit être ressaisie chaque fois que le bit de mode 12/24 heures est modifié.

Lors de la lecture ou de l'écriture des registres d'heure et de date, des tampons secondaires (utilisateur) sont utilisés pour éviter les erreurs lors de la mise à jour des registres internes. Lors de la lecture des registres d'heure et de date, les tampons utilisateur sont synchronisés avec les registres internes. Les informations temporelles sont lues à partir de ces registres secondaires pendant que l'horloge continue de fonctionner. Cela élimine le besoin de relire les registres au cas où les registres internes seraient mis à jour pendant une lecture. La chaîne de diviseur est réinitialisée chaque fois que le registre des secondes est écrit. Les transferts d'écriture se produisent sur l'accusé de réception I2C du DS1307. Une fois la chaîne de diviseur réinitialisée, pour éviter les problèmes, les registres d'heure et de date restants doivent être écrits dans la seconde..

|

Table 2. Timekeeper Registers |

||||||||||

|

ADDRESS |

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

FUNCTION |

RANGE |

|

00h |

CH |

10 Seconds |

Seconds |

Seconds |

00–59 |

|||||

|

01h |

0 |

10 Minutes |

Minutes |

Minutes |

00–59 |

|||||

|

02h |

0 |

0 → 24h |

10 Hour |

Hours |

Hours |

00–23 |

||||

|

1 → 12h |

AM / PM |

10 Hour |

1–12 + AM/PM |

|||||||

|

03h |

0 |

0 |

0 |

0 |

0 |

DAY |

Day |

01–07 |

||

|

04h |

0 |

0 |

10 Date |

Date |

Date |

01–31 |

||||

|

05h |

0 |

0 |

0 |

10 Month |

Month |

Month |

01–12 |

|||

|

06h |

10 Year |

Year |

Year |

00–99 |

||||||

|

07h |

OUT |

0 |

0 |

SQWE |

0 |

0 |

RS1 |

RS0 |

Control |

— |

|

08h–3Fh |

|

|

|

|

|

|

|

|

RAM 56 x 8 |

00h–FFh |

CONTROL REGISTER / REGISTRE DE CONTRÔLE

The DS1307 control register is used to control the operation of the SQW/OUT pin.

Le registre de contrôle DS1307 est utilisé pour contrôler le fonctionnement de la broche SQW/OUT.

|

BIT 7 |

BIT 6 |

BIT 5 |

BIT 4 |

BIT 3 |

BIT 2 |

BIT 1 |

BIT 0 |

|

OUT |

0 |

0 |

SQWE |

0 |

0 |

RS1 |

RS0 |

Bit 7: Output Control (OUT) / Contrôle de sortie (OUT).

- This bit controls the output level of the SQW/OUT pin when the square-wave output is disabled. If SQWE = 0, the logic level on the SQW/OUT pin is 1 if OUT = 1 and is 0 if OUT = 0. On initial application of power to the device, this bit is typically set to a 0.

- Ce bit contrôle le niveau de sortie de la broche SQW/OUT lorsque la sortie d'onde carrée est désactivée. Si SQWE = 0, le niveau logique sur la broche SQW/OUT est 1 si OUT = 1 et est 0 si OUT = 0. Lors de la mise sous tension initiale de l'appareil, ce bit est généralement défini sur 0.

Bit 4: Square-Wave Enable (SQWE) / Activer le signal carré (SQWE).

- This bit, when set to logic 1, enables the oscillator output. The frequency of the square-wave output depends upon the value of the RS0 and RS1 bits. With the square-wave output set to 1Hz, the clock registers update on the falling edge of the square wave. On initial application of power to the device, this bit is typically set to a 0.

- Ce bit, lorsqu'il est au niveau haut logique, active la sortie de l'oscillateur. La fréquence de la sortie d'onde carrée dépend de la valeur des bits RS0 et RS1. Avec la sortie d'onde carrée réglée sur 1 Hz, les registres d'horloge se mettent à jour sur le front descendant de l'onde carrée. Lors de la mise sous tension initiale de l'appareil, ce bit est généralement défini sur 0.

Bits 1 and 0: Rate Select (RS[1:0]) / Sélection du débit (RS[1:0]).

- These bits control the frequency of the square-wave output when the square-wave output has been enabled. The following table lists the square-wave frequencies that can be selected with the RS bits. On initial application of power to the device, these bits are typically set to a 1.

- Ces bits contrôlent la fréquence de la sortie d'onde carrée lorsque la sortie d'onde carrée a été activée. Le tableau suivant répertorie les fréquences d'onde carrée qui peuvent être sélectionnées avec les bits RS. Lors de la mise sous tension initiale de l'appareil, ces bits sont généralement définis sur 1.

|

RS1 |

RS0 |

SQW/OUT OUTPUT |

SQWE |

OUT |

|

0 |

0 |

1Hz |

1 |

X |

|

0 |

1 |

4.096 kHz |

1 |

X |

|

1 |

0 |

8.192 kHz |

1 |

X |

|

1 |

1 |

32.768 kHz |

1 |

X |

|

X |

X |

0 |

0 |

0 |

|

X |

X |

1 |

0 |

1 |

I2C DATA BUS

The DS1307 supports the I2C protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS1307 operates as a slave on the I2C bus.

Le DS1307 prend en charge le protocole I2C. Un dispositif qui envoie des données sur le bus est défini comme un émetteur et un dispositif recevant des données comme un récepteur. Le composant qui contrôle le message est appelé un maître. Les composants contrôlés par le maître sont appelés esclaves. Le bus doit être contrôlé par un dispositif maître qui génère le signal d'horloge série (SCL), qui contrôle l'accès au bus et génère les conditions START et STOP. Le DS1307 fonctionne comme esclave sur le bus I2C.

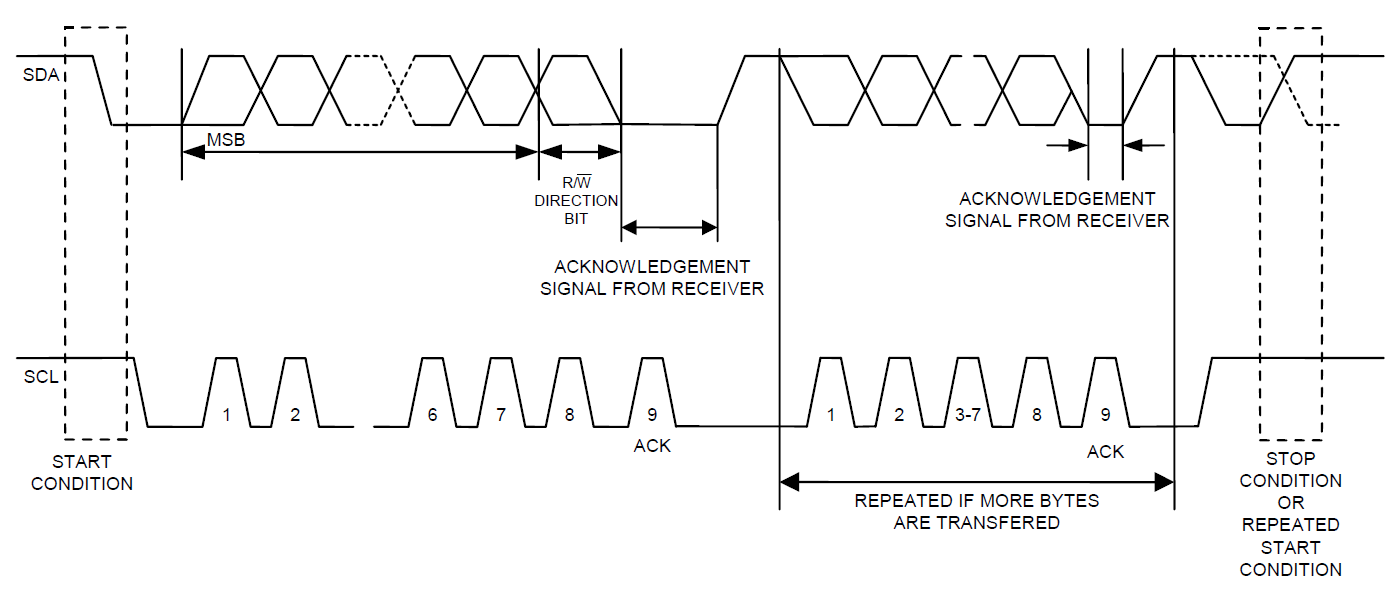

Figures 3, 4, and 5 detail how data is transferred on the I2C bus.

- Data transfer can be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

Bus not busy:

- Both data and clock lines remain HIGH.

- Les lignes de données et d'horloge restent au niveau HAUT.

START data transfer:

- A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

- Un changement d'état de la ligne de données (SDA), du niveau HAUT au niveau BAS, alors que l'horloge (SCL) est au niveau HAUT, définit une condition START.

STOP data transfer:

- A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

- Un changement d'état de la ligne de données (SDA), du niveau BAS au niveau HAUT, alors que l'horloge (SCL) est au niveau HAUT, définit une condition STOP.

Data valid:

- The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

- L'état de la ligne de données représente des données valides lorsque, après une condition START, la ligne de données est stable pendant la durée de la période HAUTE du signal d'horloge. Les données sur la ligne doivent être modifiées pendant la période BASSE du signal d'horloge. Il y a une impulsion d'horloge par bit de données.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit. Within the I2C bus specifications a standard mode (100kHz clock rate) and a fast mode (400kHz clock rate) are defined. The DS1307 operates in the standard mode (100kHz) only.

Chaque transfert de données est lancé avec une condition START et terminé avec une condition STOP. Le nombre d'octets de données transférés entre les conditions START et STOP n'est pas limité et est déterminé par le dispositif maître. Les informations sont transférées octet par octet et chaque récepteur accuse réception avec un neuvième bit. Dans les spécifications du bus I2C, un mode standard (fréquence d'horloge de 100 kHz) et un mode rapide (fréquence d'horloge de 400 kHz) sont définis. Le DS1307 fonctionne uniquement en mode standard (100 kHz).

Acknowledge:

- Each receiving device, when addressed, is obliged to generate an acknowledge after the reception of each byte. The master device must generate an extra clock pulse which is associated with this acknowledge bit.

- Chaque composant récepteur, lorsqu'il est adressé, est obligé de générer un accusé de réception après la réception de chaque octet. Le dispositif maître doit générer une impulsion d'horloge supplémentaire qui est associée à ce bit d'acquittement.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

Un dispositif qui accuse réception doit abaisser la ligne SDA pendant l'impulsion d'horloge d'accusé de réception de manière à ce que la ligne SDA soit stable au niveau BAS pendant la période HAUTE de l'impulsion d'horloge liée à l'accusé de réception. Bien sûr, les temps d'installation et de maintien doivent être pris en compte. Un maître doit signaler une fin de données à l'esclave en ne générant pas de bit d'acquittement sur le dernier octet qui a été cadencé hors de l'esclave. Dans ce cas, l'esclave doit libérer la ligne de données (Haut) pour permettre au maître de générer la condition STOP.

|

Figure 3. Data Transfer on I2C Serial Bus |

|

|

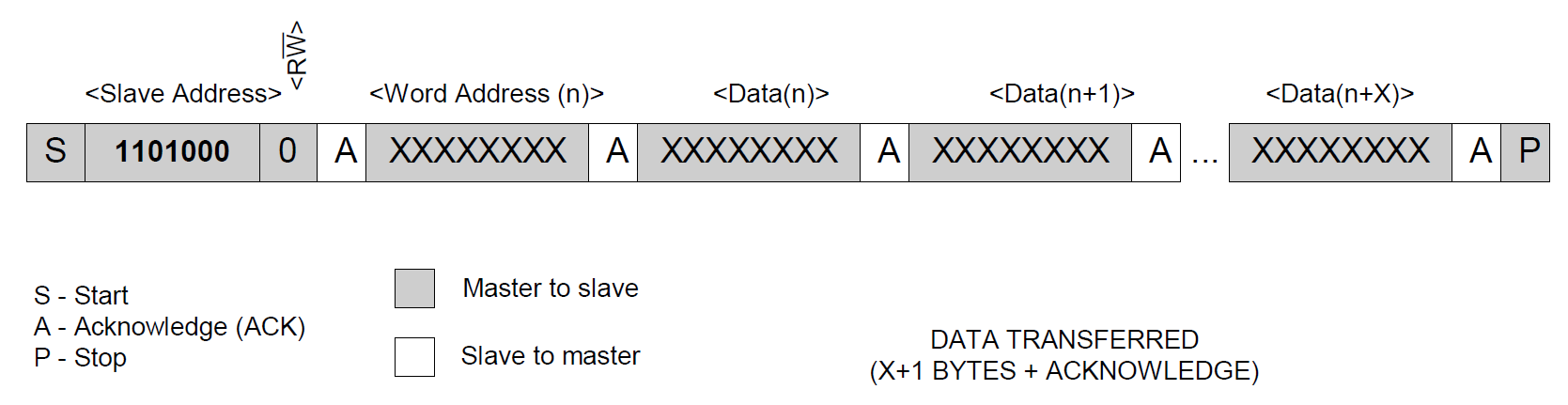

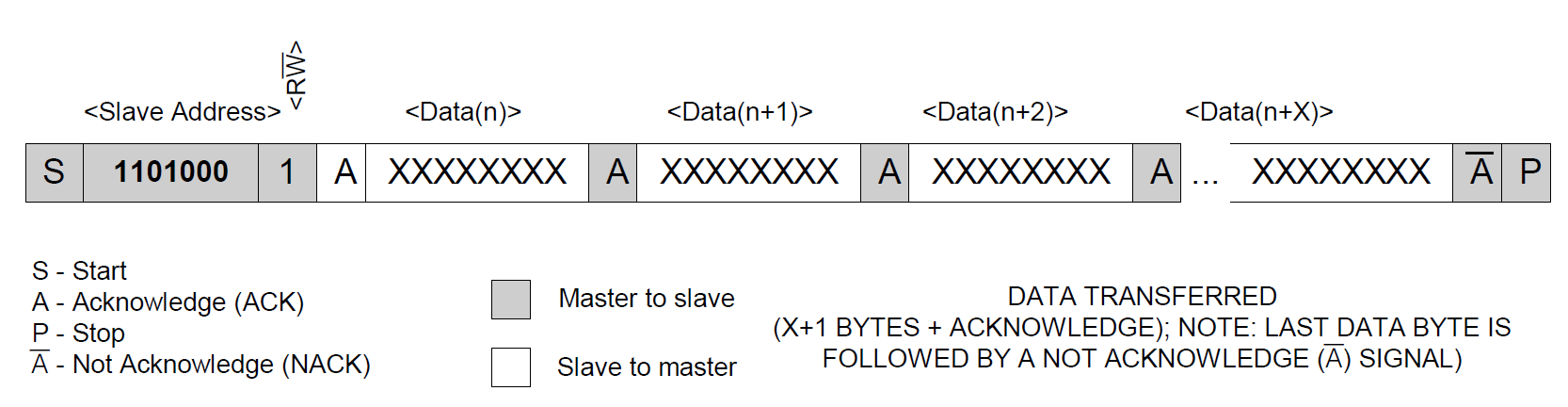

Depending upon the state of the R/W bit, two types of data transfer are possible:

1. Data transfer from a master transmitter to a slave receiver. The first byte transmitted by the master is the slave address. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. Data is transferred with the most significant bit (MSB) first.

2. Data transfer from a slave transmitter to a master receiver. The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. This is followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a “not acknowledge” is returned.

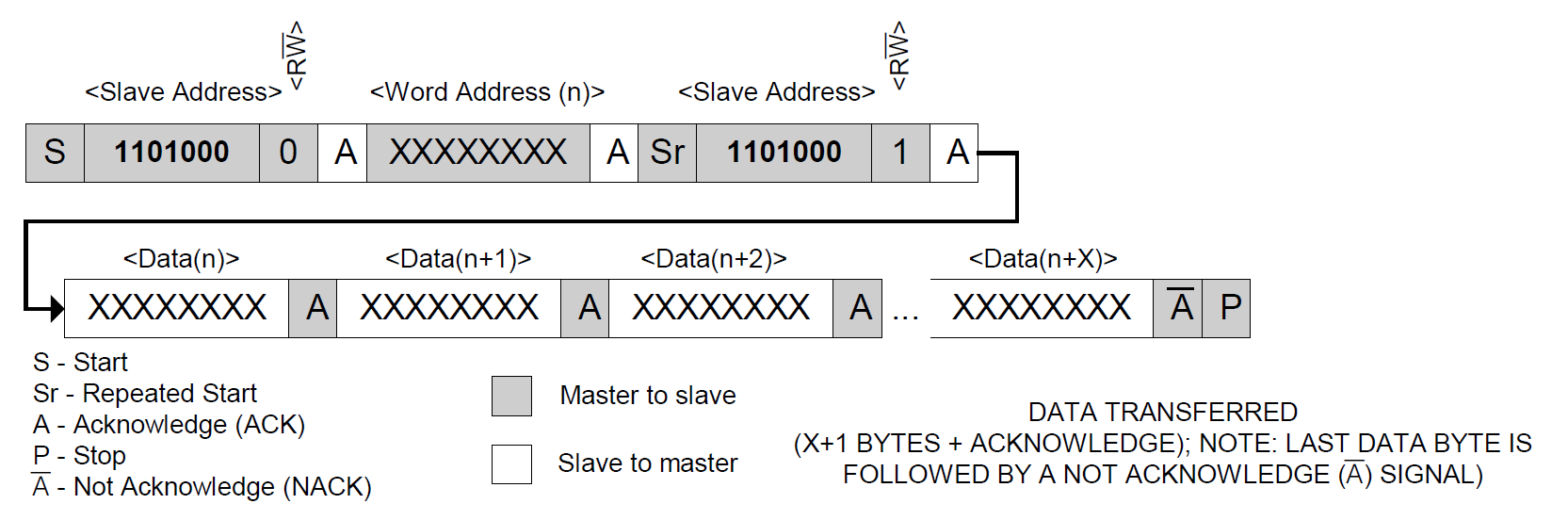

The master device generates all the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released. Data is transferred with the most significant bit (MSB) first.

The DS1307 can operate in the following two modes:

1. Slave Receiver Mode (Write Mode): Serial data and clock are received through SDA and SCL. After each byte is received an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Hardware performs address recognition after reception of the slave address and direction bit (see Figure 4). The slave address byte is the first byte received after the master generates the START condition. The slave address byte contains the 7-bit DS1307 address, which is 110 1000, followed by the direction bit (R/W), which for a write is 0. After receiving and decoding the slave address byte, the DS1307 outputs an acknowledge on SDA. After the DS1307 acknowledges the slave address + write bit, the master transmits a word address to the DS1307. This sets the register pointer on the DS1307, with the DS1307 acknowledging the transfer. The master can then transmit zero or more bytes of data with the DS1307 acknowledging each byte received. The register pointer automatically increments after each data byte are written. The master will generate a STOP condition to terminate the data write.

2. Slave Transmitter Mode (Read Mode): The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit will indicate that the transfer direction is reversed. The DS1307 transmits serial data on SDA while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer (see Figure 5). The slave address byte is the first byte received after the START condition is generated by the master. The slave address byte contains the 7-bit DS1307 address, which is 110 1000, followed by the direction bit (R/W), which is 1 for a read. After receiving and decoding the slave address the DS1307 outputs an acknowledge on SDA. The DS1307 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The register pointer automatically increments after each byte are read. The DS1307 must receive a Not Acknowledge to end a read.

|

Figure 4. Data Write—Slave Receiver Mode |

|

|

|

Figure 5. Data Read—Slave Transmitter Mode |

|

|

|

Figure 6. Data Read (Write Pointer, Then Read)—Slave Receive and Transmit |

|

|

En résumé et pour l'instant

- Le circuit " Dallas DS1307 " ou " Maxim Integrated DS1307 " est une horloge temps réel (Real Time Clock), qui fournit secondes, minutes, heures, jours, dates, mois et années.

- Les années bissextiles sont prises en compte (jusqu'en 2100).

- Le DS1307 travaille dans le mode standard du bus I2C (fréquence d'horloge de 100 kHz).

- L'adresse I2C (7 bits) du DS1307 est : 0b1101000 soit 0x68 (adresse fixée par le constructeur et non modifiable).

l'adresse I2C 8bits est donc pour une écriture (W) 0b1101 0000 soit 0xD0

l'adresse I2C 8bits est donc pour une lecture (R) 0b1101 0001 soit 0xD1

Créé avec HelpNDoc Personal Edition: Faites de la création de fichiers d'aide CHM un jeu d'enfant avec HelpNDoc