|

La Bascule R/ S/ |

LES BASCULES ASYNCHRONES

La Bascule R S

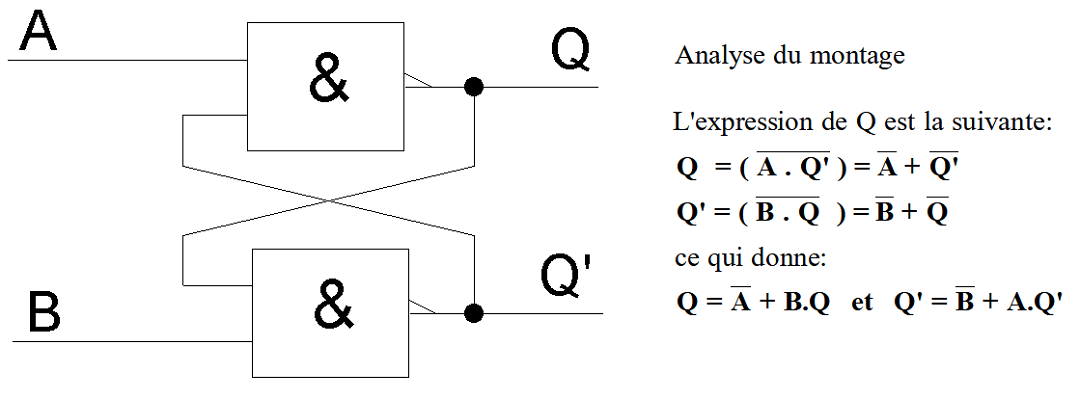

Soit le montage suivant

|

|

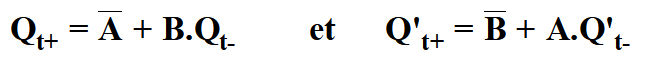

Cette expression montre bien que l'état de la sortie Q dépend de A et B, mais aussi de son état initial. L' expression peut donc se réécrire en faisant intervenir la variable temps.

Phase 1: A=0 et B=1 Qt+ = 1 et Q't+ = 0

mise à l'état haut de la sortie Q

Phase 2: A=1 et B=1 Qt+ = Qt- et Q't+ = Q't - de plus Q' = Q

cette phase représente l'état mémoire de la bascule

Phase 3: A=1 et B=0 Qt+ = 0 et Q't+ = 1

mise à l'état bas de la sortie Q

Phase 4: A=0 et B=0 Qt+ = 0 et Q't+ = 0

L' entrée A, active à l'état bas, sera appelée S, S pour Set , mise à 1. L'entrée B, aussi active à l'état bas, sera appelée R, R pour Reset, remise à 0.

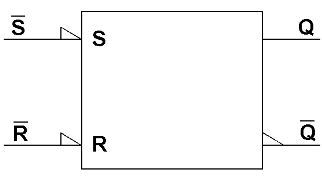

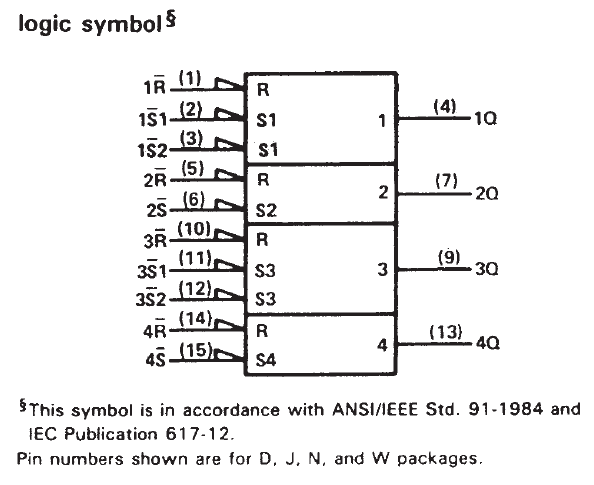

De plus si l'on excepte la phase 4, on peut écrire pour les autres phases Q = Q', la représentation symbolique de cette bascule est alors la suivante

|

Symbole électrique (norme IEEE / IEC) |

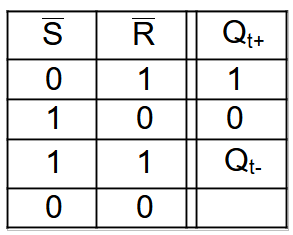

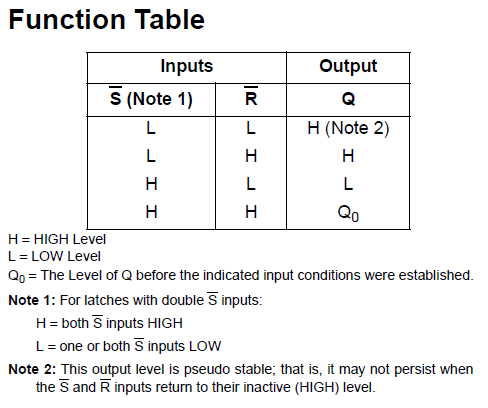

Table de fonctionnement |

|

|

|

|

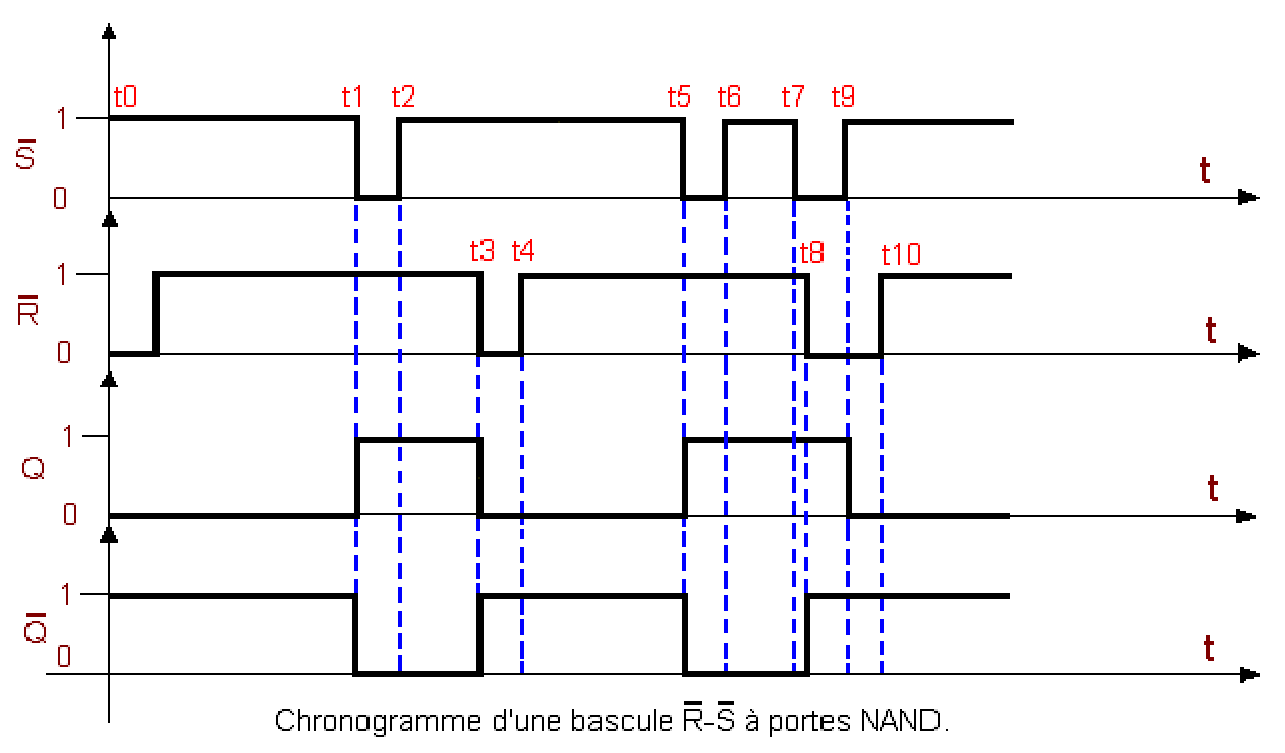

Chronogramme de fonctionnement |

|

|

Simulation (Proteus 7)

le schéma structurel version Proteus 7.xx R_S_NAND.DSN

le schéma structurel version Proteus 8.xx R_S_NAND.pdsprj

Cette bascule fonctionne correctement mais il existe un cas où il y a risque d'instabilité comme le montre la vidéo suivante

Cette instabilité a lieu lorsque les deux entrées passent simultanément de l'état actif (R = S = 0) à l'état inactif (R = S = 1).

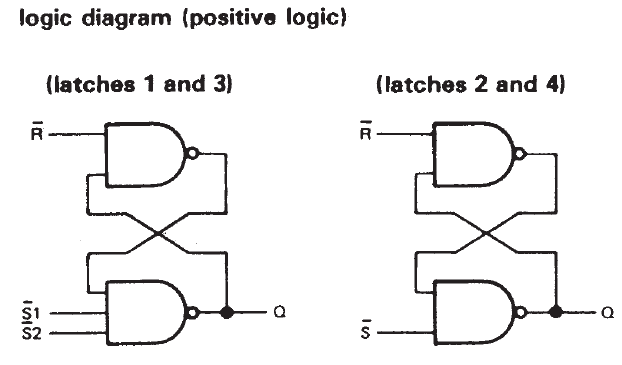

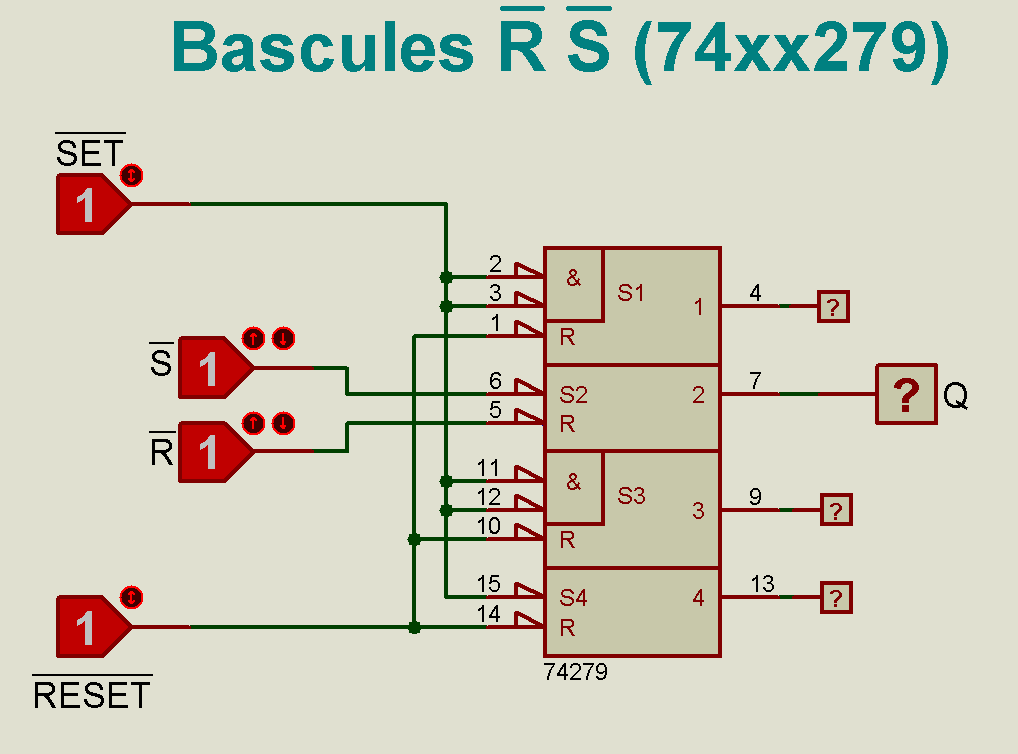

Exemple de composant (74xx279) DM74LS279.PDF

|

DM74LS279 Quad S/ - R/ Latch General Description The DM74LS279 consists of four individual and independent Set-Reset Latches with active low inputs. Two of the four latches have an additional S input ANDed with the primary S input. A LOW on any S input while the R input is HIGH will be stored in the latch and appear on the corresponding Q output as a HIGH. A LOW on the R input while the S input is HIGH will clear the Q output to a LOW. Simultaneous transition of the R and S inputs from LOW-to-HIGH will cause the Q output to be indeterminate. Both inputs are voltage level triggered and are not affected by transition time of the input data. |

|

|

|

|

Créé avec HelpNDoc Personal Edition: Créer des documents d'aide HTML facilement