|

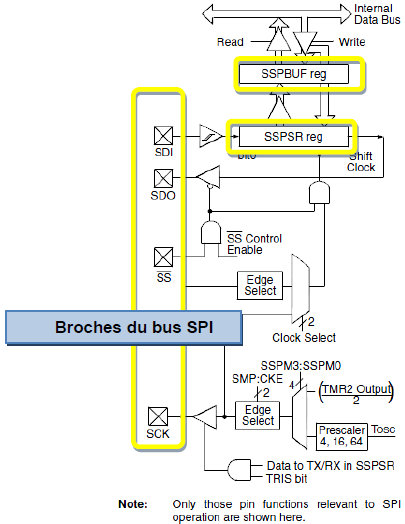

Constitution pour un système PIC |

Constitution pour un système à microcontrôleur PIC

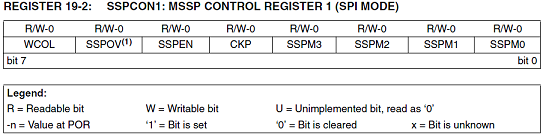

Le MSSP Control Register 1 (SSPCON1)

|

bit 7 WCOL |

: Write Collision Detect bit (Transmit mode only) 1 = Le registre SSPBUF register est écrit pendant que l'octet prévu est transmis (Doit être effacé par le programme) 0 = Pas de détection |

|

bit 6 SSPOV |

: Receive Overflow Indicator (*1) SPI mode esclave: 1 = un nouvel octet est reçu pendant que le registre SSPBUF est encore en possession de l'ancien. En cas de débordement (overflow) la donnée du SSPSR est perdue. Le débordement n'intervient que dans le mode Esclave. L'utilisateur doit lire le SSPBUF, seulement en cas de transmission de donnée, pour éviter le maintien de l'overflow il doit être effacer dans le soft. 0 =Pas de débordement |

|

bit 5 SSPEN |

: Master Synchronous Serial Port Enable 1 = validation de la configuration SCK, SDO, SDI et SS comme port série (*2) 0 = pas de validation du mode SPI, les broches sont en E/S normales (*2) |

|

bit 4 CKP |

: Clock Polarity Select bit 1 = horloge au niveau haut logique au repos 0 = horloge au niveau bas logique au repos |

|

bit 3-0 SSPM3:SSPM0 |

: Master Synchronous Serial Port Mode Select bits 0101 = SPI mode Esclave, clock = SCK, SS non validée, SS peut être utilisée en E/S(3) 0100 = SPI mode Esclave, clock = SCK , SS (select slave) validée 0011 = SPI mode Maître, clock = TMR2 output/2 0010 = SPI mode Maître , clock = FOSC/64 0001 = SPI mode Maître , clock = FOSC/16 0000 = SPI mode Maître , clock = FOSC/4 |

Note:

(*1) : Dans le mode Maître , le bit de dépassement n'est pas mis à 1 à chaque transmission ou nouvelle réception mais est initialisé par une écriture dans le registre SSPBUF.

(*2) : Si validé, cette broche doit être configuré comme une entrée ou une sortie.

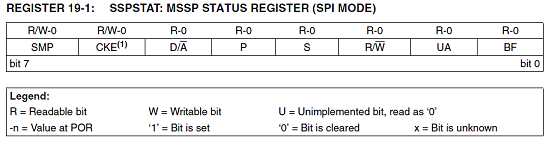

Le MSSP Status Register (SSPSTAT)

|

bit 7 SMP |

: Sample bit Dans le mode Maître 1 = Échantillonnage de la donnée entrante à la fin du temps de sortie de la données sortante 0 = Échantillonnage de la donnée entrante au milieu du temps de sortie de la données sortante Dans le mode Esclave mis à 0 |

|

bit 6 CKE |

: SPI Clock Select bit 1 = Transmission sur front de l'état actif vers état repos de l'horloge 0 = Transmission sur front de l'état repos vers état actif de l'horloge Dans le mode Esclave mis à 0 |

|

bit 0 BF |

: Buffer Full Status bit (Receive mode only) 1 = Réception complète, SSPBUF plein 0 = Réception incomplète , SSPBUF vide |

Les bits 1, 2, 3, 4 et 5 ne sont pas utilisés en mode SPI.

Le Serial Receive/Transmit Buffer Register SSPBUF

Ce registre est utilisé pour lire ou écrire les données de / vers l'extérieur du PIC.

Le MSSP Shift Register

|

Ce registre n'est pas accessible en direct ! Ce registre est utilisé pour recevoir / envoyer les données de / vers l'extérieur du PIC. Pendant les opérations de transmission, les 2 registres SSPSR et SSPBUF créent un double tampon receveur, lorsque le SSPSR à reçu un octet, il le transfère au SSPBUF en provoquant la mise à 1 de SSPIF |

|

Créé avec HelpNDoc Personal Edition: Maximisez la protection de vos PDF en suivant ces étapes simples