|

Le Bus SPI |

Propriétés physiques du bus SPI

Le support physique

Les caractéristiques de fonctionnement du bus SPI

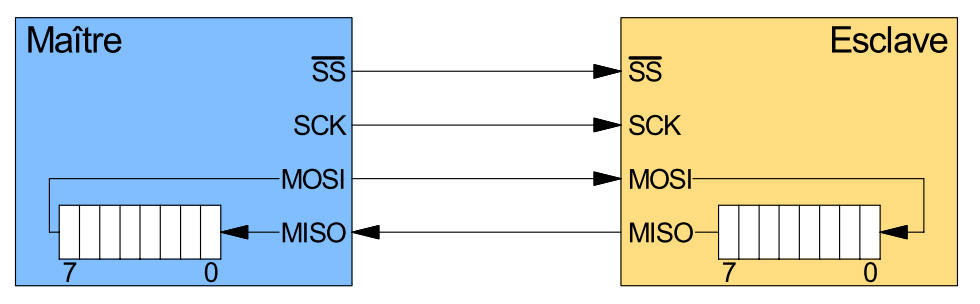

Les données échangées sont des octets. La transmission s’effectue sur 2 fils monodirectionnels (nommés MOSI, MISO). Une horloge indépendante fixée par le maître synchronise les échanges (en général sur front). La fréquence de l’horloge de transmission est comprise entre 1 MHz et 20 MHz (selon les performances des circuits reliés au bus). Il n’y a pas d’adressage des esclaves (comme sur un bus I2C par exemple). L’esclave devient actif au moyen d’une ligne de sélection de boîtier dédiée (généralement active à l'état bas). La ligne est constituée de 3 fils auxquels il faut ajouter les fils de sélection d'esclave.

|

|

SCLK (serial clock) : Horloge du bus (produite par le maître) MOSI (Master Out Slave In) : Données du maître vers l’esclave actif MISO (Master In Slave Out) : Données de l’esclave actif vers le maître SSn (Slave Select n) : Sélection de l'esclave n à destination de la transmission |

La fréquence d'horloge de transmission (maître) est paramétrable :

Par exemple pour un AT80C5112 en mode maître, les 3 bits du registre SPCON (Serial Peripheral CONtrol register) SPR2, SPR1 et SPR0 permettent de choisir parmi 7 fréquences, obtenues par division de la fréquence de l’horloge du microcontrôleur.

|

SPR2 |

SPR1 |

SPR0 |

Fréquence de l’horloge SPI |

|

0 |

0 |

0 |

Fμc/2 |

|

0 |

0 |

1 |

Fμc/4 |

|

0 |

1 |

0 |

Fμc/8 |

|

0 |

1 |

1 |

Fμc/16 |

|

1 |

0 |

0 |

Fμc/32 |

|

1 |

0 |

1 |

Fμc/64 |

|

1 |

1 |

0 |

Fμc/128 |

Synoptique d'une liaison SPI Maître-Esclave

On utilise le principe du registre à décalage. Dans le cas ci-dessus, en 8 périodes d'horloge, l'octet passe du registre du maître à celui de l'esclave et réciproquement le contenu du registre d'esclave est passé dans celui du maître (full-duplex : simultanéité des transferts). Puisqu’il ne peut pas y avoir de collisions lors du transfert, il n'y a pas besoin d'arbitrage.

Lien avec le modèle OSI

La couche 2 est réalisée par le contrôleur SPI intégré dans un microcontrôleur.

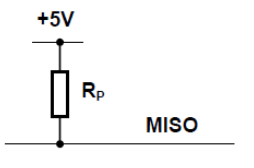

Polarisation de la ligne MISO

Lorsque le bus est inutilisé, ce qui revient à dire qu’aucun esclave n’est sélectionné, la ligne MISO est à l’état haute impédance, ce qui ne permet pas d’en définir l’état logique.

On évite cela par l’utilisation d’une résistance (Rp) de polarisation, de 5 kΩ à 50 kΩ, qui n’a aucune influence sur la vitesse de transmission (contrairement à ce qui se passe pour un bus I2C).

Format de transfert de données

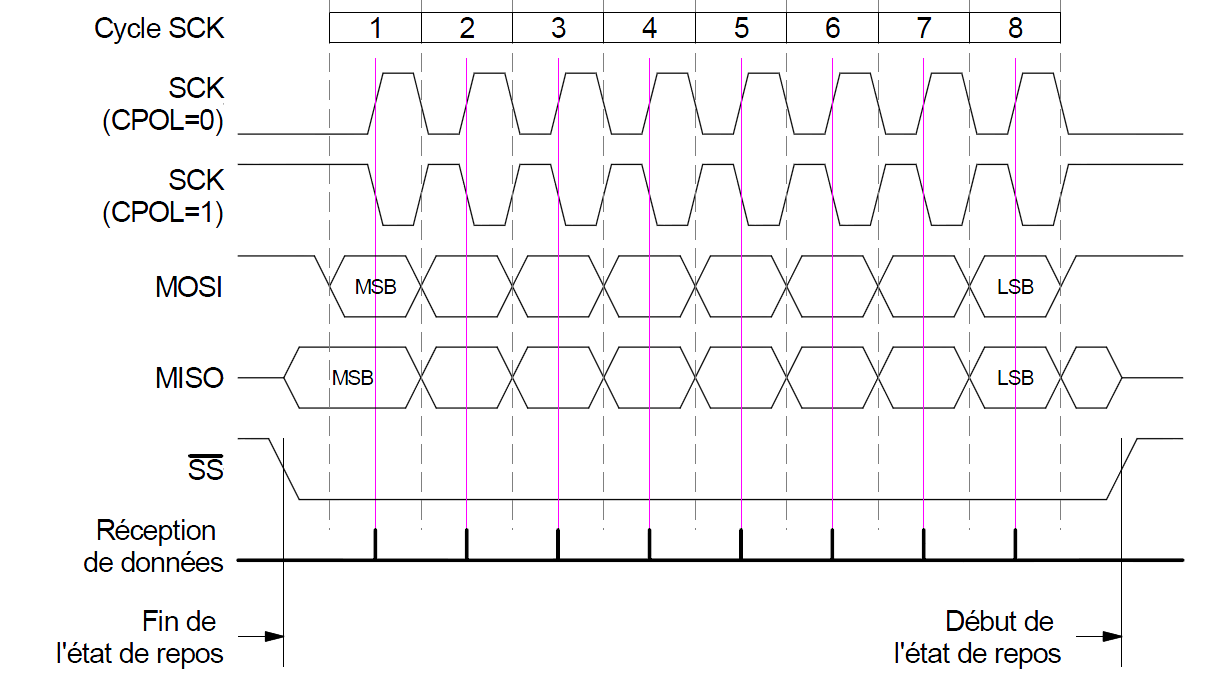

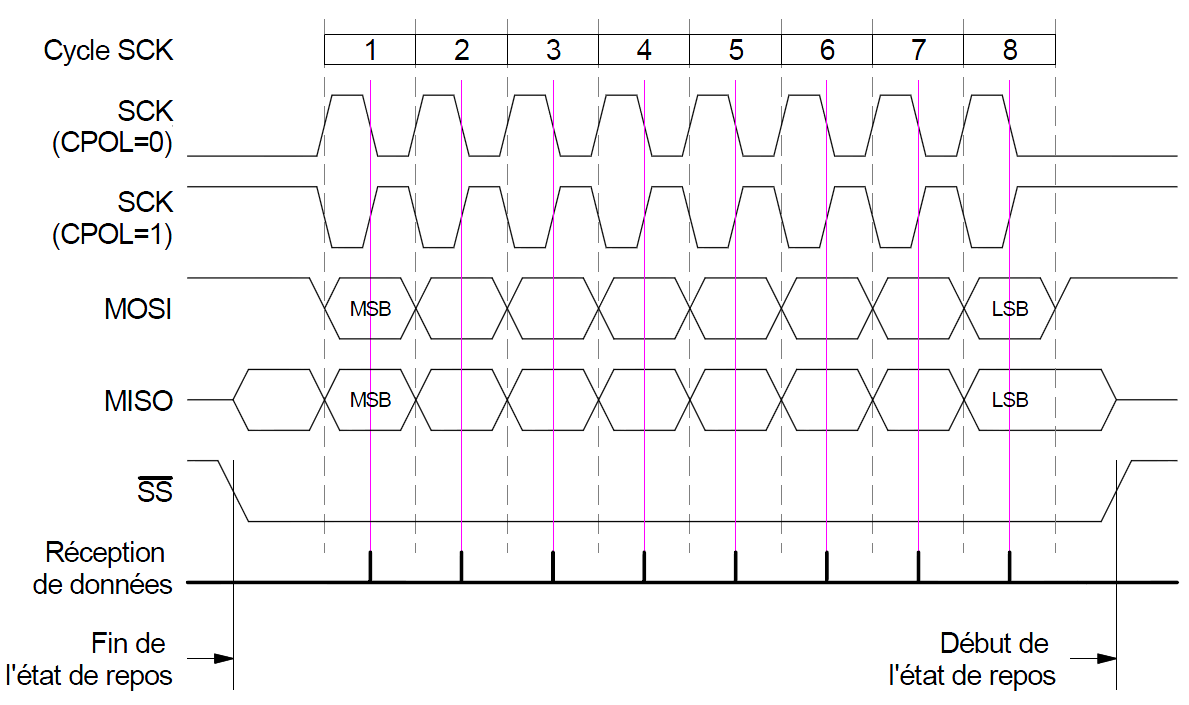

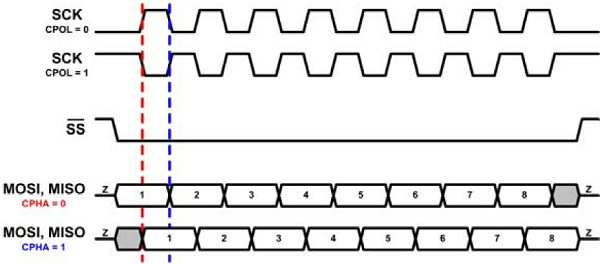

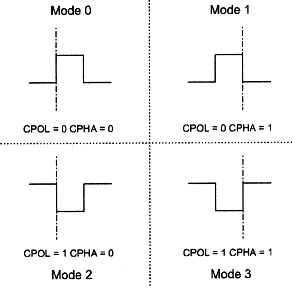

Lorsque CPHA = 0, les données sont valides au premier front du signal d’horloge. La polarité CPOL détermine s’il s’agit d’un front montant ou descendant.

En effet, pour CPOL=0, au repos, l’horloge est au niveau BAS; le premier front est donc un front montant.

Pour CPOL=1, au repos, l’horloge est sur le niveau HAUT; le premier front est donc un front descendant.

La polarité de l’horloge n’ayant pas d’influence sur le moment où le premier bit de données est valide elle n’a pas d’effet sur le format du transfert de données (voir figure ci-dessous).

Lorsque CPHA = 1, les données sont réceptionnées avec le deuxième front du signal d’horloge.

Pour CPOL=0, au repos, l’horloge est au niveau BAS et monte au niveau HAUT après le premier front, le deuxième front est donc un front descendant.

Pour CPOL=1, au repos, l’horloge est au niveau HAUT et descend au niveau BAS après le premier front; le deuxième front est donc un front montant.

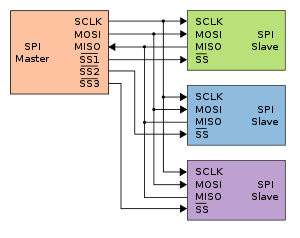

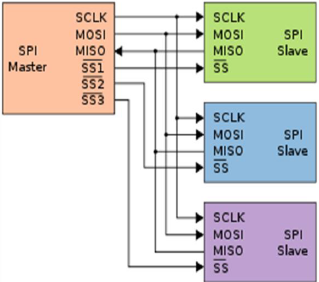

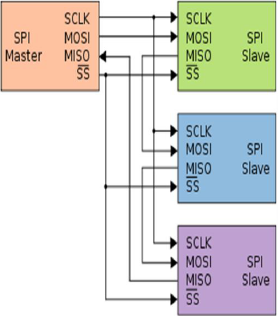

Synoptique d'une liaison SPI Maître-Multi-Esclaves

|

|

Le maître sélectionne un seul et unique esclave avec lequel il veut rentrer en communication par la mise à niveau logique zéro de SS (1 2 3), puis, après 8 fronts d'horloge, l'octet de donnée est transféré. La patte MISO de l'esclave non sélectionné est à l'état haute impédance. La seule limite au nombres d'esclaves est en fait la possibilité de broches SS du maître. |

|

|

Cas de la "daisy chain" (esclave en guirlande, en cascade...) Le maître sélectionne tous les esclaves par la mise à niveau logique zéro de SS , puis après 3*8 fronts d'horloge, les 3 octets de données sont transférés (dans le cas d’un octet par esclave). Cette disposition permet de réduire le nombre de lignes SS, mais en contre partie il faudra un "buffer" plus grand dans le maître (ou une gestion du soft plus élaborée). |

Avantages et Inconvénients du bus SPI :

|

Avantages |

Inconvénients |

|

Communication en Full Duplex |

Pas d'adressage possible |

|

"Indépendant" du nombre de bits à transmettre |

Utilisation sur très courte distance (même carte) |

|

Pas de collision possible |

Nécessite plus de fils que I²C |

|

Les esclaves utilisent l'horloge du maître pas de problème de précision de quartz |

Pas d'acquittement (le maître ne sait pas s’il est écouté) |

|

Beaucoup plus rapide que I²C en mode standard |

|

|

Possibilité de configuration à plusieurs maîtres |

|

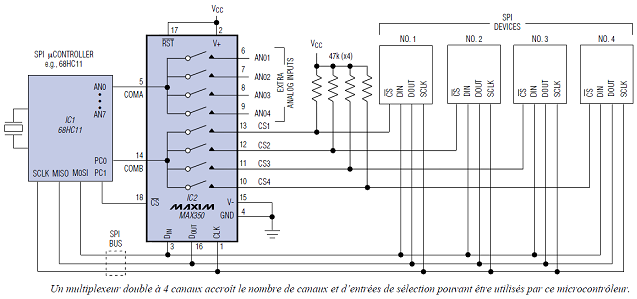

Niveaux électriques du Bus SPI

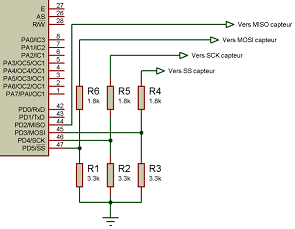

Les niveaux de tension des signaux échangés sont compatibles TTL/CMOS. Il pourra-t-être envisagé dans certains cas de placer des résistances de pull-up de 47kΩ (voir ci-dessous : utilisation d'un multiplexeur MAXIM MAX350).

|

Si on utilise des composants de tension d'alimentation différente par exemple un μprocesseur alimenté sous 5V et un capteur alimenté en 3,3V, il convient de procéder à une adaptation du niveau de tension des broches MOSI, SS, SCLK (la broche MISO n'est pas affectée car compatible avec le μp) par diviseur de tension à base de résistance ¼ de watt. |

|

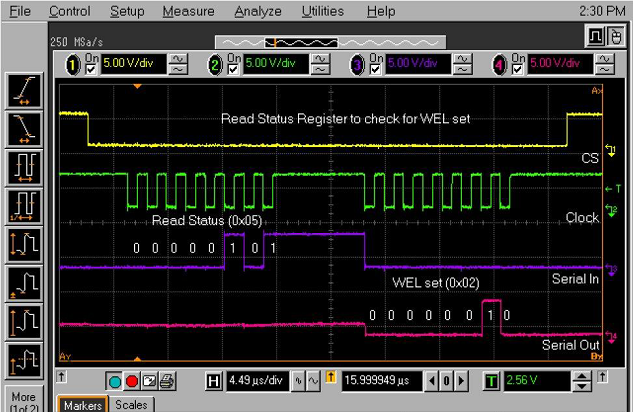

Oscillogrammes des signaux électriques SPI

Chronogramme

Toutes les liaisons SPI respectent le chronogramme général ci-dessous, mais quatre variantes existent au niveau de la prise en compte des données qui sont échangées.

Chronogramme général d’un échange sur une liaison SPI

Ces variantes sont parfois appelées modes SPI et sont alors numérotées de 0 à 3. En présence d’un circuit à interface SPI, il vous suffira de comparer sa fiche technique avec le chronogramme pour savoir dans quel « mode » il fonctionne. Ces quatre modes sont définis par la polarité de l’horloge, appelée CPOL (Clock POLarity), qui peut-être égale à 0 ou à 1, et par la phase de cette même horloge, appelée CPHA (Clock PHAse), par rapport aux données, qui peut être aussi égale à 0 ou à 1. Cela conduit aux quatre possibilités, qui indiquent sur quel front du signal d’horloge les données sont échantillonnées et peuvent donc être considérées comme valides. Par défaut, le mode le plus courant est appelé mode 0, c’est-à-dire celui ou CPOL et CPHA sont tous les deux nuls.

Créé avec HelpNDoc Personal Edition: Avantages d'un outil de création d'aide