|

Mise en œuvre d'une communication |

Exemple de mise en œuvre d'une communication

Nous prendrons pour exemple l'échange d'une donnée au format d'un octet. En effet à ce stade de la mise en œuvre, il faut avoir à l'esprit que dans la plupart des cas c'est le périphérique esclave qui va imposer au maître le format de la trame, car il s'agit pour le MCU de piloter un composant externe afin d'étendre ces capacités. Il existe donc de nombreux périphériques esclave intégrant une liaison SPI, comme des mémoires, des ADC ou DAC, des RTC, etc...

Imaginons alors d’implémenter le firmware d'un périphérique SPI esclave sur la carte d'un CPLD. Le mode 0 étant le plus répandu, nous le choisirons avec une trame de 1 octet. Chaque octet qu'il recevra du maître sera alors copier vers 8 LED et comme la liaison est Full duplex, nous pouvons imaginer de définir 8 entrées dont les valeurs seront transmise par l'esclave.

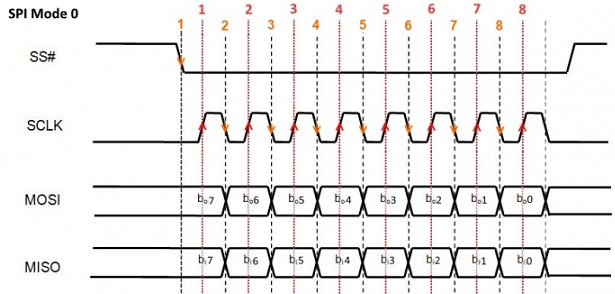

Pour commencer, observons le chronogramme des signaux de la liaisons SPI, avec en rouge l’échantillonnage des données sur les fronts montant du signal SCLK et en orange l'état transitoire des données sur les fronts descendants:

On peut décomposer la communication en trois phases:

- Début de la communication

Le maître du bus SPI, ici la carte PIC, met le signal SS à 0 de façon à indiquer à l'esclave que la communication commence (Slave Select est actif à l'état bas). Ce signal SS est très important et souvent négligé dans l'implémentation des algorithmes.

Coté microcontrôleur en mode maître SPI, il ne fait pas partie du module interne (uniquement dans le mode esclave) et doit-être définit par le développeur qui devra alors réserver autant de ligne SS qu'il y aura d'esclave avec lesquels communiquer.

Coté CPLD la détection du front descendant de ce signal va permettre d'initialiser les signaux et registres internes avant le premier coup d'horloge, le bit 7 doit alors imposer sont état sur la ligne MISO.

- Acquisition et transfert des bits

Le maître fera ensuite basculé huit fois le signal d'horloge.

Sur les fronts montants, l'esclave enregistre les données provenant du signal MOSI et le maître mémorise sur la ligne MISO la valeur de chaque bit provenant de l'esclave, c'est le Full duplexe.

Les données sur les lignes MOSI/MISO sont ensuite mise à jour sur les fronts descendants du signal SCLK.

- Fin de la communication

Le maître tire la ligne SS à l'état haut pour indiquer que le transfert est terminé.

Les différents autres noms utilisés avec un bus SPI

- SCK :

Il s'agit de l'horloge de synchronisation des échanges, elle est générée par le maître et est commune à tous les éléments du bus. Cela a pour avantage d’éviter que chaque composant possède son propre quartz avec les problèmes de précision que cela impose.

- SDI, DI, SI, SDO, DO, SO :

Il s'agit de la patte de Serial Data In; dans ce cas de convention d'écriture il convient de relier la SDI du maître à la SDO du ou des esclaves.

Il s'agit de la patte de Serial Data Out; dans ce cas de convention d'écriture il convient de relier la SDO du maître à la SDI du ou des esclaves.

- nCS, CS ,nSS, STE :

Il s'agit de la patte SS Slave Select générée par le maître.

- QSPI Queued Serial Peripheral Interface :

C'est un type de contrôleur dédié et spécifique qui permet certains transferts de données sans l'utilisation du processeur, mais en faisant appel à des pointeurs programmables, pointant une file d'attente de données.

Ce n'est pas un autre type de bus série.

Créé avec HelpNDoc Personal Edition: Maximisez votre productivité avec les fonctionnalités de création de fichiers d'aide CHM de HelpNDoc