Conçu à l'origine pour relier les circuits intégrés d'une même platine, ce moyen d'interconnexion est aussi très utilisé pour relier

les différents éléments d'un système

tel que les "organes" d'un robot ou d'une machine numérique et se retrouve même à la base d'installations domotiques.

Le bus I²C est caractérisé par une liaison en mode série réalisée à l'aide de 2 fils. C'est la société Philips qui en a créé le concept au début des années 80. Son succès est lié à sa simplicité.

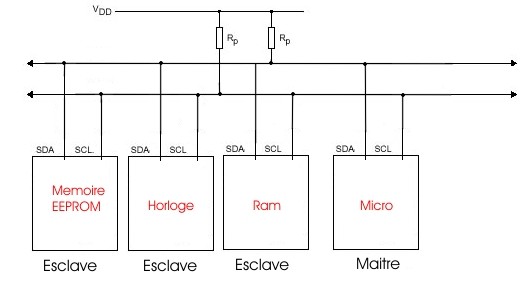

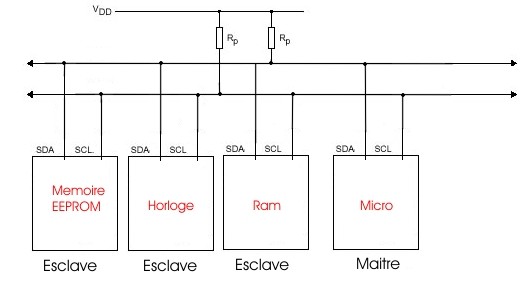

Voici l'architecture type d'un bus I²C: on remarque que plusieurs composants viennent se "greffer" sur le même bus.

Les données transitent par les lignes:

-SDA (signal de donnée Serial Data Line, transfert des données bi-directionnel, synchrone avec SCL) généré par le Maître ou l'Esclave.

-SCL (signal d'horloge Serial Clock Line, horloge de transmission synchrone, fournie par le micro-contrôleur et commune à tous les récepteurs)

généré par le Maître.

La communication sur le bus est orchestrée de la manière suivante:

-Le Maître envoie sur le bus l'adresse du composant avec qui il souhaite communiquer, chacun des esclaves ayant une adresse fixe, l'esclave qui

se reconnait répond à son tour par un signal de confirmation, puis le Maître continue la procédure de communication (écriture/lecture).

Dans tous les cas, les transactions seront confirmées par un ACK.

Les dispositifs qui viennent se connecter au bus se raccordent en parallèle sur les lignes SDA et SCL. La discussion sur un bus se fait entre un

Maître et un Esclave. C'est le Maître qui demande et l'Esclave qui répond. Un Esclave peut être Maître si sa structure interne le permet.

Electroniquement, la mise en place de plusieurs composants sur un même bus est possible grâce à a structure des sorties qui sont de type

"Collecteur ouvert".

Des résistances de rappel (Rp) permettent de garantir l'état haut du bus lorsque les éléments sont en mode haute indépendance, sorte de similitude

à un élément non existant.

Son calcul s'effectue en fonction de la charge capacitive et reste relativement simple.

Les résistances RS sont présentes pour protéger le circuit contre les pics de tension produit par induction, son calcul restant relativement

compliqué et peu utilisé.

Cependant, le nombre de composants étant limité sur le bus, celui-ci ne peut fontionner qui si la charge capacitive est inférieure à 400 pF,

cela correspondà une distance de 10m.

A titre indicatif, un composant varie entre 10 et 20 pF de charge capacitive.

Si cette charge venait à être atteinte, il existe un composant (bridge 82B71S) permettant de réaliser un pont entre une partie déjà saturée

et une autre plus libre.

Tension du bus: 5V DC

Fréquence maximale de fonctionnement: 400 kHz (variable suivant les composants connectés au bus, voir datasheet).

Etat logique haut: de 3V à 5V

Etat logique bas: de 0V à 1,5V

Capacité maximum admissible sur le bus: 400 pF (picoFarad)

Temps de monté des signaux: inférieur à 1µs

Temps de stabilité pour prise en compte d'un signal: supérieur à 5µs (règle générale)

Résistance de rappel: à calculer en fonction de l'impédance du bus (valeurs pratiques constatées de 1k à 4,7k)

Distance de communication: Quelques dizaines de cm, et plusieurs mètres avec un tampon

Le bus I²C est un bus de type sériel permettant la communication de composants électroniques.

Il existe d'autres bus de ce type:

-Le Cbus de Philips qui est l'ancêtre de ce bus.

-Le bus SPI de Motorola.

-Le bus µWire de National SemiConducteur.

Standarisé en 1992 dans sa version première, ce bus a été implémenté des caractéristiques suivantes:

Programmation logicielle des adresses esclaves. Le mode "Lent" a été révisé en mode normal, les composants se réglant à la plus lente discussion

sur le bus. Le mode "Fast" a été ajouté pour permettre une communication à 400kbps, celui-ci étant compatible avec les composants communicant à

100kbps. L'adresse des composants est passée de 8 Bits à 10 Bits ajoutant ainsi 1024 adresses possibles. L'ajout de filtres antiparasites

dans les composants.

En 1998, ce bus est devenu un nouveau standard dans plus de 1000 composants différents et a été licencié par plus de 50 entreprises différentes.

Aujourd'hui, beaucoup d'applications requièrent un bus rapide et de faible alimentation, les ajoutsont donc été les suivants:

Le mode "Highspeed" permettant la communication à 3,4Mbps a été ajouté. Les tensions de seuils ont été ajustées à 2V permettant ainsi

une réduction de l'immunité aux bruits.

Datant de janvier 2000, il s'agit de la version actuelle constituant des modifications mineures touchant les conditions de départ du mode "Highspeed".

Le protocole de ce bus va être décrit dans sa version 2.1, même s'il n'a pas subi de changement significatif depuis sa version initiale

(mode high-speed uniquemnt).

Ce protocole est défini par la succession des états que peuvent prendre les signaux SDA et SCL. Ce protocole est relativement simple et

puissant à la fois.

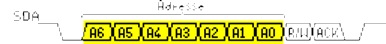

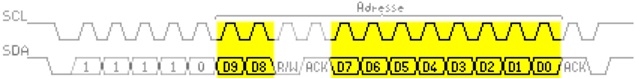

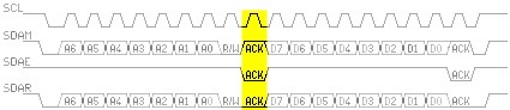

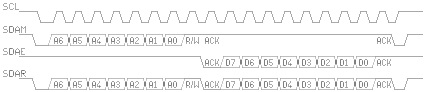

En fait, il est possible de décomposer cette trame en 2 parties:

les Bits de A6 à ACK peuvent être vus comme la première partie et ceux de D7 à ACK comme la seconde.

Ces 2 parties n'étant que la mise en place de l'adresse destinataire et de la donnée transmise ou reçue.

Avant d'initier un dialogue sur le bus, chaque composant doit s'assurer que le bus est libre.

Pour ce faire, le composant maître vérifie que es lignes SDA et SCL sont au repos (état haut) et ce pendant une durée de 4,7µs, temps

constructeur désigné par THD, STA.

Toujours présente, la condition de "start" est définie par un changement de la ligne de donnée alors même qu'elle n'a pas été validée

par l'horloge.

La condition pour initier ce départ étant l'état "1" sur les lignes SDA et SCL.

La condition de "start" a lieu lors du passage de la ligne de donnée à "0" alors même que l'horloge reste à "1".

Il s'agit ici du morceau de trame qui comporte les plus grandes traces de l'histoire bu bus I²C.

Dans sa forme primitive, le CBUS, il a fallu adapter l'adresse 10 Bits des nouveles versions du Bus I²C avec son histoire.

On peut voir sur le schéma ci-dessus que l'adressage se fait du bit le plus fort vers le bit le plus faible, le huitième bit sera décrit dans

la section suivante.

L'établissement d'une adresse sur 10 bits s'effectue en 2 temps:

Dans un premier temps, on envoie un octet comprenant les 2 bits de poids forts de l'adresse.

Le quartet premier ne doit comporter que des 1 et le second quartet commence par un 0, les 2 bits représentant

les 2 bits de poids forts de l'adressage sur 10 bits, le dernier étant celui de lecture/écriture.

Le maître doit maintenant attendre le bit de validation, il peut être donné par plusieurs composants à la fois, tous ceux commençant par cette

adresse.

La seconde partie de l'adresse sera donc transmise une fois l'accusé reçu.

Il existe plusieurs variantes de cette méthode d'adressage car, notamment sur les mémoires, il faut effectuer un adressage interne du composant,

cette seconde adresse étant transmise après l'accusé de la première adresse.

Afin de répondre à certaines fonctions du bus, il est nécessaire d'avoir des adresses spécifiques permettant des opérations particulières.

Si l'adresse est à 0 et le bit de lecture/écriture à 0, il s'agit d'un rappel général ou plus communément appelé BroadCast.

Si l'adresse est à 0 et le bit de lecture/écriture à 1, il s'agit d'un "otet de départ", il peut être envoyé avant le transfert réel afin

de palier aux problèmes des composants les plus lents, notamment ceux simulant le protocole de manière logicielle.

Plus communément appelé R/W, il s'agit du huitième bit du premier octet.

Il sera toujours mis en bit de poids le plus faible de l'octet de l'adresse.

Son utilité réside dans le fait d'indiquer à l'esclave appelé s'il s'agit d'une lecture ou d'une écriture qui sera effectuée.

Effectué par l'esclave, ce bit permet de signaler au maître qu'il existe bien un composant à l'adresse indiquée.

Son utilisation est un peu spéciale et n'est possible que par la technologie électronique mise en oeuvre dans le concept du bus I²C.

Le maître doit maintenir la ligne SDA à l'état haut, l'esclave mettra à bas la ligne SDA, il ne reste donc plus qu'au maître

à lire l'état de la ligne SDA.

Il n'existe pas de normalisation du délai après lequel l'esclave sera considéré comme inexistant.

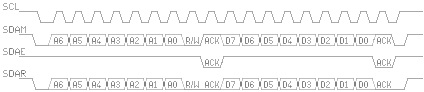

légende:

SCL-> Horloge du bus

SDAM-> Niveaux imposés par le maître

SDAE-> Niveaux imposés par l'esclave

SDAR-> Niveaux résultant sur le bus

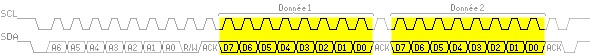

Il s'agit de la deuxième partie de la trame; elle contient les données circulant sur le bus.

S'il s'agit d'une lecture, le maître met à "1" le niveau du SDA et l'esclave se charge de descendre à "0" ce niveau pour former l'octet résultant

d'une lecture, chaque bit étant bien entendu délimité par l'horloge SCL.

S'il s'agit d'une écriture, le niveau du SDA va être contrôlé par le maître, l'escave écoutant en appliquant un niveau haut sur le bus.

Dans le cas où les données seraient plus importantes en lecture ou en écriture, la seconde partie de la trame (donnée + ACK) est répétée

autant de fois que nécessaire.

Il s'agit de nouveau d'un accusé de réception, mais de la donnée cette fois-ci.

Cependant, selon s'il s'agit d'une écriture où d'une lecture, le niveau de ce bit varie.

En effet, lors d'une lecture, ce bit est à "1" car l'esclave n'a pas à accuser le fait qu'il ait fini d'envoyer ces données.

Lors d'une écriture, l'esclave met à "0" le niveau du bus, donnant ainsi un accusé de réception de la donnée.

Ceci est une notion importante faisant la spécificité de cet acquittement par rapport à ceui de l'adresse.

La condition de "stop" est à l'inverse de la condition de "start". La réalisation de cette condition sous-entend au préalable que les

lignes SDA et SCL soient au niveau "0".

Cette condition remplie, la ligne SDA passe au niveau "1", puis c'est au tour de la ligne SCL e passer au niveau "1".

Une fois ce signal donné, tous les composants sont dans un état de veille et ne réagiont qu'à la prochaine condition de "start".