Harvard

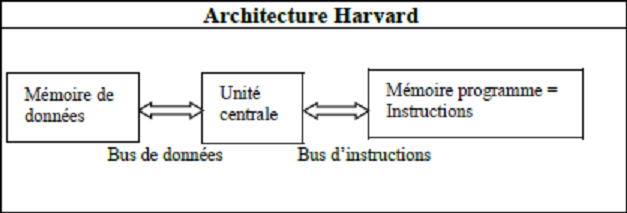

L’architecture de type Harvard est une conception de microprocesseurs qui sépare physiquement la mémoire de données et la mémoire programme. L’accès à chacune des deux mémoires s’effectue via deux bus distincts.L’architecture Harvard est souvent utilisée dans : les processeurs numériques de signal (DSP soit "Digital Signal Processor") ; les microcontrôleurs, notamment les PIC de Microchip et les AVR d'Atmel.

En effet, l’exécution d’une instruction ne fait plus appel qu’à un seul cycle machine puisque l’on peut simultanément, grâce aux deux bus, rechercher le code de l’instruction et la ou les données qu’elle manipule. Rompant avec une tradition bien établie, les microcontrôleurs PIC ou Microchip, toutes familles confondues, utilisent une architecture de type RISC qui, comme on le lit un peu trop souvent, ne se résume pas simplement à disposer d’un jeu d’instructions réduit.

Von Neumann

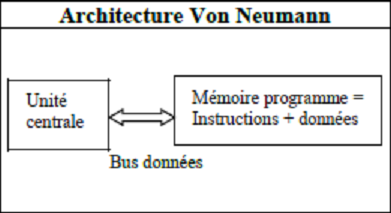

De nos jours, de nombreux microprocesseurs et micro contrôleurs utilisent une architecture interne dite de Von Neumann, c'est a dire en fait une architecture commune à celle que l'on rencontre habituellement dans les micro-ordinateurs. La mémoire appelée improprement de programmes, contient des instructions et des données placées à la suite les unes des autres et l'on ne dispose que d'un bus, appelé bus de données, son but est de véhiculer tour à tour les codes des instructions et les données qui leur sont associées.

John von Neumann est né en 1903 à Budapest et est mort en 1957, il était reconnu en tant que mathématicien et physicien. Il a apporté d'importantes contributions en mécanique quantique, en analyse fonctionnelle, en informatique ainsi que dans beaucoup d'autres domaines des mathématiques et de la physique. Il a de plus participé aux programmes militaires américains (calcul et étude lors de la construction de la bombe Fat Man larguée sur Nagasaki). Von Neumann a donné son nom à l'architecture de von Neumann utilisée dans la quasi totalité des ordinateurs modernes.

Les points forts de l’architecture RISC

Les processeurs RISC font reposer l'optimisation du code sur le compilateur, tandis que les instructions sont faciles à décoder pour le processeur. Pour cela :- Ces processeurs disposent de beaucoup de registres généraux (au moins 16, généralement 32) pour faciliter leur allocation par le compilateur.

- Les instructions sont de taille fixe, souvent 32 bits.

- Les instructions arithmétiques ont généralement 3 adresses : 2 registres servant d'opérandes et un registre de sortie.

- Les accès à la mémoire font l'objet d'instructions spécifiques, et une valeur doit d'abord être chargée dans un registre pour être utilisée : on parle d'architecture load-store ou d'instructions register-register.